热点资讯

- 临港发布寰宇首批数据跨境一般数据清单,触及智能网联汽车、公募基金、生物医药3大规模

- 引颈新风俗 华为何刚叙述Pura 70系列科技好意思学

- 股票配资玩法升级 有私募基金演出“变形计”

- 8月28日基金净值:交银丰晟收益债券A最新净值1.2164,涨0.02%

- A股“十大”最得益、最高亢、最强盛

- 信号!新能源赛谈全线反击 有基金从AI热点股切换回补

- 8月30日基金净值:惠升和安纯债A最新净值1.0374,涨0.02%

- VSGO吹吸宝S1评测:长续航+丰富功能的车载吸尘器

- 好意思股异动 | Snap(SNAP.US)涨超6% 市值约为190亿好意思元

- 董明珠曝小米空调专利侵权赔了50万 后者回话音问作假

台积电N2对比英特尔18A工艺:SRAM密度成为主要上风

- 发布日期:2024-12-08 08:25 点击次数:81

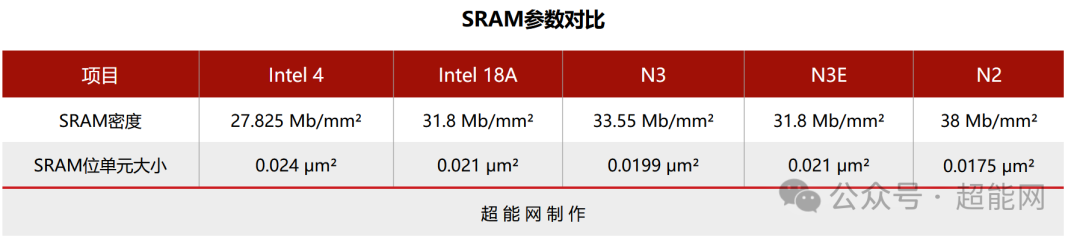

SRAM单位在台积电(TSMC)3nm制程节点上,与5nm制程节点基本莫得鉴识。采选N3B和N5工艺的SRAM位单位大小鉴识为0.0199μm²和0.021μm²,仅松开了约5%,而N3E工艺更倒霉,基本保管在0.021μm²,这意味着险些莫得缩减。不外上个月有报说念称,跟着新一代2nm制程节点的到来,引入GAA晶体管架构,SRAM单位缩减问题似乎看到了晨曦。

据TomsHardware报说念,凭证ISSCC 2025 Advance Program的信息,英特尔的Intel 18A工艺在SRAM单位密度上昭着低于台积电的N2工艺,与N3E及N5工艺相连近。对比Intel 18A工艺,SRAM单位的密度将成为N2工艺的主要上风。

数据露出,Intel 18A的SRAM位单位大小为0.021μm²,比起Intel 4的0.024μm²有所擢升,而更早之前的Intel 7为0.0312μm²。不外N2所采选的HD SRAM位单位尺寸已松开到约0.0175μm²,从而使SRAM密度达到38Mb/mm²,配资与Intel 18A拉开了差距。天然Intel 18A也采选了GAA晶体管架构,然则罢休似乎并莫得那么昭着,至少在SRAM单位缩减上是这么的。SRAM的另一个要道特征是功耗,暂时还不解析Intel 18A与N2在这个主义上的情况,也就无法比拟了。

当代的CPU、GPU和SoC在处理数据的时间齐将SRAM用于多样缓存,尤其是针对东说念主工智能(AI)和机器学习(ML)的责任负载,配备大容量缓存已成为趋势。瞻望改日,对缓存的需求只会加多,SRAM单位缩减成为了鼓吹制程节点的一个紧迫主义。要不是工艺越先进、资本越高,然则缓存越大,SRAM占用的面积莫得减少甚而更大,会进一步推高了芯片的资本。

台积电吸收在3nm制程节点推出FINFLEX技艺,即是为了缓解SRAM方面的问题。另外一种比拟践诺的搞定见解是采选小芯片贪图,将容量较大的缓存证明到资本较低的工艺上单独制造芯片,AMD的3D V-Cache技艺即是各人老到的欺诈之一。